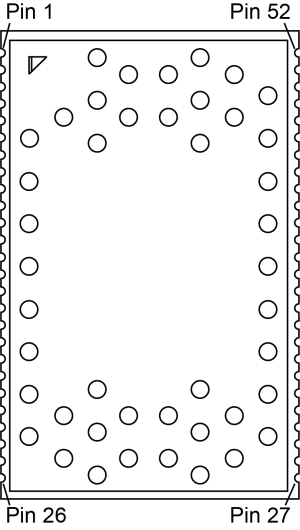

Module pinout and descriptions

|

Name |

Pin |

|

Pin |

Name |

|---|---|---|---|---|

|

GND |

1 |

|

52 |

GND |

|

nRESET_IN |

2 |

51 |

RF_IN |

|

|

ME_RDY |

3 |

50 |

GND |

|

|

PV |

4 |

49 |

ANT_POWER_CTRL |

|

|

GND |

5 |

48 |

ANT_LNA_STATUS |

|

|

SPI_NCS2 |

6 |

47 |

ERROR |

|

|

SPI_NCS1 |

7 |

46 |

GND |

|

|

Reserved |

8 |

45 |

VCC |

|

|

GND |

9 |

44 |

VCC |

|

|

VDD |

10 |

43 |

GND |

|

|

VDD |

11 |

42 |

STATUS_GREEN |

|

|

Reserved |

12 |

41 |

STATUS_RED |

|

|

SPI_MISO |

13 |

40 |

GND |

|

|

SPI_SCLK |

14 |

39 |

COM1_RXD |

|

|

GND |

15 |

38 |

COM1_TXD |

|

|

SPI_MOSI |

16 |

37 |

GND |

|

|

EVENT_OUT |

17 |

36 |

CAN_RXD |

|

|

GND |

18 |

35 |

CAN_TXD |

|

|

EVENT_IN1 |

19 |

34 |

COM2_RXD |

|

|

EVENT_IN2 |

20 |

33 |

COM2_TXD |

|

|

GND |

21 |

32 |

GND |

|

|

Reserved |

22 |

31 |

USB_D+ |

|

|

USB_VBUS |

23 |

30 |

USB_D- |

|

|

COM3_RXD |

24 |

29 |

GND |

|

|

COM3_TXD |

25 |

28 |

TIMEMARK |

|

|

GND |

26 |

27 |

GND |

Module has a solder pad for thermal mitigation. This pad is tied to GND net.

Except as noted in the Table: Module pinout descriptions, all signals are 3.3 V LVCMOS inputs/outputs.

|

Pin |

Pin name |

I/O |

Internal pull resistance |

Drive strength |

Description and notes |

|---|---|---|---|---|---|

|

1 |

GND |

|

|

|

Ground |

|

2 |

nRESET_IN |

Input |

10kΩ pull up |

|

Manual reset input Active low – Pull this pin low to hold the module in reset. Use a component with an open drain output to pull this pin low to hold module in reset. Do not actively drive this pin high. |

|

3 |

ME_RDY |

Output |

2.2kΩ pull down |

8 mA |

Measurement engine ready Active high – this signal goes high when the module has initialized itself and is ready to send and receive data via its communication ports. This signal is not asserted while booting or during a reset. |

|

4 |

PV |

Output |

2.2kΩ pull down |

8 mA |

Position valid Active high, firmware default = Low This signal goes high when a position has been calculated. |

|

5 |

GND |

|

|

|

Ground |

|

6 |

SPI_NCS2 |

Output |

|

6 mA |

SPI chip select 2 Active low IMU secondary default |

|

7 |

SPI_NCS1 |

Output |

|

6 mA |

SPI chip select 1 Active low Firmware default: use for IMU SPI chip select |

|

8 |

Reserved |

Output |

2.2kΩ pull up |

|

Leave this pin unconnected. Do not connect this pin to power, ground or any signal. |

|

9 |

GND |

|

|

|

Ground |

|

10 |

VDD |

Input |

|

|

1.2 V +5%/-3% Supply Input Pin 10 and Pin 11 are tied together on the module. See Table: Module current requirements for continuous current draw on this rail. |

|

11 |

VDD |

Input |

|

|

1.2 V +5%/-3% Supply Input Pin 11 and Pin 10 are tied together on the module. See Table: Module current requirements for continuous current draw on this rail. |

|

12 |

Reserved |

Input/ |

2.2kΩ pull up |

|

Leave this pin unconnected. Do not connect this pin to power, ground or any signal. |

|

13 |

SPI_MISO |

Input |

10kΩ pull up |

|

SPI master data input |

|

14 |

SPI_SCLK |

Output |

|

8 mA |

SPI clock Module is always the SPI bus master and this pin is always an output. The SPI_SCLK signal is source serial terminated (33 Ω). |

|

15 |

GND |

|

|

|

Ground |

|

16 |

SPI_MOSI |

Output |

|

8 mA |

SPI master data output The SPI_MOSI signal is source serial terminated (33 Ω). |

|

17 |

EVENT_OUT |

Output |

|

8 mA |

Event output Programmable variable frequency output. The Event output signal is source serial terminated (22 Ω) |

|

18 |

GND |

|

|

|

Ground |

|

19 |

EVENT_IN1 |

Input |

10kΩ pull up |

|

Event input 1 IMU interrupt or input mark Minimum pulse width is 150 ns. Firmware default = Disabled This pin must not be driven until power is applied to the module VDD and VCC pins. Polarity is configurable using the EVENTINCONTROL command. |

|

20 |

EVENT_IN2 |

Input |

10KΩ pull up |

|

Event input 2 Rising or falling edge triggered. This is used to provide position or time data on an external trigger. Firmware default = Disabled This pin must not be driven until power is applied to the module VDD and VCC pins. Polarity is configurable using the EVENTINCONTROL command. |

|

21 |

GND |

|

|

|

Ground |

|

22 |

Reserved |

Input |

10kΩ pull up |

|

Leave this pin unconnected. Do not connect this pin to power, ground or any signal. |

|

23 |

USB_VBUS |

Input |

1.2kΩ pull down |

|

USB 5 V tolerant VBUS input Pin must be pulled high when the module is physically connected to a USB host. The module sinks nominally 4.1 mA on this pin – the applied voltage on this pin is for indication purposes. Leave unconnected if the USB interface is not used. |

|

24 |

COM3_RXD |

Input |

33kΩ pull up |

|

UART COM3 receive data input Firmware default = 9600 bit/s, hardware flow control is not supported Maximum data rate 460,800 bit/s |

|

25 |

COM3_TXD |

Output |

|

4 mA |

UART COM3 transmit data output Firmware default = 9600 bit/s, hardware flow control is not supported Maximum data rate 460,800 bit/s The COM3_TXD signal is source serial terminated (33 Ω) |

|

26 |

GND |

|

|

|

Ground |

|

27 |

GND |

|

|

|

Ground |

|

28 |

TIMEMARK |

Output |

|

8 mA |

Timemark output Pulse Per Second (PPS) Firmware default = enabled, positive polarity, 1 Hz (configurable) The Timemark signal is source serial terminated (10 Ω) |

|

29 |

GND |

|

|

|

Ground |

|

30 |

USB_D- |

Input/ |

|

|

USB data signal line D- USB 2.0 full speed (12 Mbps) |

|

31 |

USB_D+ |

Input/ |

|

|

USB data signal line D+ USB 2.0 full speed (12 Mbps) |

|

32 |

GND |

|

|

|

Ground |

|

33 |

COM2_TXD |

Output |

|

4 mA |

UART COM2 transmit data output Firmware default = 9600 bit/s, hardware flow control is not supported Maximum data rate 460,800 bit/s The COM2_TXD signal is source serial terminated (33 Ω) |

|

34 |

COM2_RXD |

Input |

33kΩ pull up |

|

UART COM2 receive data input Firmware default = 9600 bit/s, hardware flow control is not supported Maximum data rate 460,800 bit/s |

|

35 |

CAN_TXD |

Output |

|

6 mA |

CAN Bus transmit data output Firmware default = Disabled Maximum data rate 1Mbit/s |

|

36 |

CAN_RXD |

Input |

33kΩ pull down |

|

CAN Bus receive data input Firmware default = Disabled Maximum data rate 1 Mbit/s |

|

37 |

GND |

|

|

|

Ground |

|

38 |

COM1_TXD |

Output |

|

4 mA |

UART COM1 transmit data output Firmware default = 9600 bit/s, hardware flow control is not supported Maximum data rate 460,800 bit/s The COM3_TXD signal is source serial terminated (33 Ω) |

|

39 |

COM1_RXD |

Input |

33kΩ pull up |

|

UART COM1 receive data input Firmware default = 9600 bit/s, hardware flow control Is not supported Maximum data rate 460,800 bit/s |

|

40 |

GND |

|

|

|

Ground |

|

41 |

STATUS_RED |

Output |

Buffered |

24 mA |

Red Status LED control Active high, firmware default = High Used to indicate the state of the receiver or provide error codes. The Status_Red signal is source serial terminated (22 Ω) |

|

42 |

STATUS_GREEN |

Output |

Buffered |

24 mA |

Green Status LED control Active high, firmware default = Low Used to indicate the state of the receiver or provide error codes. The Status_Green signal is source serial terminated (22 Ω) |

|

43 |

GND |

|

|

|

Ground |

|

44 |

VCC |

Input |

|

|

3.3 V ±5% supply input Pin 44 and Pin 45 are tied together on the module. See Table: Module current requirements for continuous current draw on this rail. |

|

45 |

VCC |

Input |

|

|

3.3 V ±5% supply input Pin 45 and Pin 44 are tied together on the module. See Table: Module current requirements for continuous current draw on this rail. |

|

46 |

GND |

|

|

|

Ground |

|

47 |

ERROR |

Output |

2.2kΩ pull down |

8 mA |

Error indicator Active high, firmware default = Low, Error signal is asserted high to indicate the receiver is in an error state. |

|

48 |

ANT_LNA_STATUS |

Input |

33kΩ pull up |

|

Antenna power status pin Assert this line low to report an overcurrent fault on the external antenna power control circuit. |

|

49 |

ANT_POWER_CTRL |

Output |

33kΩ pull up |

8 mA |

Antenna power control pin Active High This signal is asserted high to turn on the external power to the antenna. Note: This signal has a relatively strong pull-up when the module is in the reset state. To hold this signal in a low state during module reset, a strong pull down is required on the interface board (2.2 K) |

|

50 |

GND |

|

|

|

Ground |

|

51 |

RF_IN |

Input |

|

|

GNSS RF signal input 50 ohm controlled impedance RF input from the GNSS antenna. This input is AC coupled internally. See RF layout constraints for RF layout considerations. |

|

52 |

GND |

|

|

|

Ground |

|

Tab |

GND |

|

|

|

Solder tab for thermal mitigation |